---

## ANÁLISE E DESENVOLVIMENTO DE UM *PLL (Phase Locked Loop)* DIGITAL, UTILIZANDO UM MICROCONTROLADOR DA FAMÍLIA C2000, PARA APLICAÇÕES EM ELETROÔNICA DE POTÊNCIA E SISTEMAS DE ENERGIA.

Francisco Rodrigues Lemes<sup>1</sup>

Luciano de Souza da Costa e Silva<sup>2</sup>

Eliézer Alves Teixeira<sup>3</sup>

<sup>1</sup>IFG/Campus Jataí/Bacharelado em Engenharia Elétrica - PIBIT, francisco-engeletrica@hotmail.com

<sup>2</sup>IFG/Campus Jataí/ Departamento de Áreas Acadêmicas, luciano.souza@ifg.edu.br

<sup>3</sup>IFG/Campus Jataí/Departamento de Áreas Acadêmicas, eliezer.teixeira@ifg.edu.br

### Resumo

Nesse artigo serão analisados os principais algoritmos de sincronização PLL (*Phase Locked Loop*). Uma maior ênfase será dada aos algoritmos de sincronização monofásicos p-PLL (*power - Phase Locked Loop*) e LPN-PLL (*Low-Pass Notch Filter - Phase Locked Loop*). Os dois sistemas de sincronização são compostos pelos mesmos blocos básicos: Detector de Fase (PD – *Phase Detector*), Filtro Passa-Baixas (LPF – *Low Pass Filter*) e Oscilador Controlado por Tensão (VCO – *Voltage Controlled Oscilator*), sendo diferenciados pelas características de implementação do bloco Detector de Fase. A análise teórica completa dos dois algoritmos de PLL citados é realizada tendo como base a teoria de sistema de controle linear no domínio da frequência. Baseado na análise teórica e em resultados de simulações computacionais, os algoritmos digitais de PLL são implementados através do Microcontrolador da *Texas Instruments TMS320F28069M*. Os ensaios em laboratório demonstram o desempenho adequado dos algoritmos implementados, em particular, no que se refere à capacidade de sincronização e obtenção da fase instantânea da componente fundamental do sinal elétrico amostrado e processado digitalmente.

**Palavras-chave:** pll, notch, microcontrolador, distúrbios, frequência.

### INTRODUÇÃO

O ingresso de fontes alternativas de energia no sistema elétrico de potência tem aumentado a complexidade dos processos e equipamentos que o compõe. Nesse contexto, a estimação de parâmetros dos sinais elétricos é uma operação primordial quando se deseja analisar o sistema do ponto de vista da sua qualidade, proteção, bem como do controle de suas grandezas (GOMES, 2007). Assim, a evolução da ciência e tecnologia tem possibilitado a utilização de computadores e *softwares* no processo de controle e monitoramento destes sistemas (SANTOS, 2010). No atual cenário do sistema elétrico, tem-se a necessidade do controle da qualidade da energia elétrica, fazendo da eletrônica de potência uma importante ferramenta nos sistemas elétricos de potência.

O avanço da eletrônica de potência têm proporcionado soluções ótimas no que se refere à qualidade da energia elétrica processada nas diversas aplicações possíveis. Dentre tais aplicações, citam-se a utilização de filtros ativos de potência, retificadores e inversores conectados à rede de distribuição de energia elétrica. (MESQUITA, 2011). Ainda, a evolução da eletrônica de potência têm permitido o controle sobre diversos processos industriais, proporcionando a automação destes através do processamento eletrônico de energia implementado pelos conversores de potência.

Na maior parte dos processos, que envolvem a aplicação da eletrônica de potência no sistema de energia elétrica, existe uma característica que é comum; os sistemas de controle utilizados nos conversores necessitam de sincronismo com as componentes fundamentais de tensões e/ou correntes do sistema elétrico. Este sincronismo é realizado através de um PLL (*Phase Locked Loop*). O PLL é um sistema de sincronização que tem por função gerar um sinal de sincronismo em fase com a componente fundamental da rede.

## PHASE LOCKED LOOP (PLL)

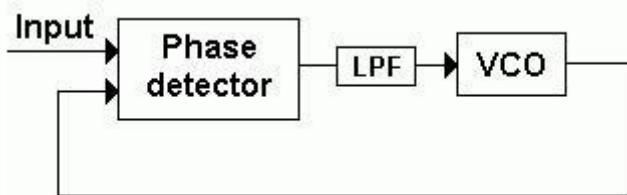

Em termos gerais, todo PLL é constituído de três blocos básicos: Detector de Fase (PD – *Phase Detector*), Filtro Passa-Baixas (LPF – *Low Pass Filter*) e Oscilador Controlado por Tensão (VCO – *Voltage Controlled Oscillator*). O que é distinto na maior parte das estruturas de PLL é a implementação do bloco detector de fase PD. Na FIGURA 1 apresenta-se o diagrama de blocos da estrutura clássica de um pll.

**FIGURA 1: PLL**

Na estrutura clássica do pll, o detector de Fase (PD) , como o próprio nome sugere, tem a função da deteção de fase, gerando um sinal de erro proporcional à defasagem entre a componente fundamental do sinal de entrada e a saída realimentada do VCO. O segundo bloco, filtro Passa-Baixas (LPF), é implementado por um controlador do tipo Proporcional-Integral (PI) que acumula duas funções; atenuar a componente de segunda harmônica proveniente da saída do bloco PD e proporcionar rastreamento perfeito do ângulo de fase do sinal da rede elétrica, mesmo sob condições de distúrbios. No terceiro bloco, o oscilador controlado por tensão (VCO) recebe um sinal contínuo do LPF, que representa as variações de frequência necessárias para o rastreamento do sinal de entrada; este sinal é somado com a frequência central de regime permanente do sistema e o resultado é integrado para gerar a rampa que representa o ângulo de fase do sinal rastreado. Assim, na saída do VCO, são disponibilizados os sinais do ângulo de fase, bem como as funções senoidais que representam o sinal em fase e o sinal ortogonal com relação a referência. O sinal ortogonal é sempre realimentado para as novas detecções de defasagem no bloco PD.

Pretende-se, neste artigo, descrever de forma geral as estruturas e algoritmos monofásicos de PLL que possam ser aplicados nas mais diversas áreas da eletrônica de potência. Dentre as estruturas de PLL descritas são implementados dois algoritmos de PLL; o p-PLL, baseado na teoria da potência instantânea, e o algoritmo LPN-PLL, similar ao p-PLL, no entanto, com a adição de um filtro *notch* adaptativo para garantir a linearização do sistema. A análise teórica dos algoritmos de PLL é realizada tendo como base as equações características de um sistema linear de segunda ordem padrão. Baseado na análise teórica e em resultados de simulações computacionais, são implementados os algoritmos digitais de PLL através do Microcontrolador da *Texas Instruments TMS320F28069M*.

## METODOLOGIA

Dentre os algoritmos citados, realizou-se o estudo e a implementação digital via microcontrolador dos algoritmos p-PLL e LPN-PLL. O estudo e análise matemática dos algoritmos foram acompanhados em simulações computacionais através de resultados numéricos e gráficos. Realizou-se a implementação digital dos algoritmos de PLL através do microcontrolador TMS320F28069M. Dois geradores de sinais, conectados nos conversores digitais/analógicos (ADC) de 12 bits do microcontrolador, emularam as características dos sinais da rede. O sinal convertido foi processado digitalmente, para ambos os algoritmos, na mesma malha de controle, com uma taxa de amostragem e processamento de 15 kHz. Além da configuração dos periféricos ADCs, configurou-se também quatro canais digitais/analógicos (DAC), implementados pelo conjunto de 4 canais de PWMs conectados à filtros passa-baixas RC, para a visualização analógica no osciloscópio das principais formas de onda do algoritmo.

## IMPLEMENTAÇÃO DOS PLLs

A implementação dos PLLs, é dada através do projeto do LPF, pois esse bloco como citado é constituído por um controlador PI (Proporcional integral).

$$K_i = \left( \frac{4}{\varepsilon t_s} \right)^2 [1]$$

$$K_p = \frac{8}{t_s} [2]$$

Sendo  $K_i$  e  $K_p$  os ganhos integral [1] e proporcional [2] respectivamente,  $t_s$  o tempo de estabelecimento e  $\varepsilon$  o coeficiente de amortecimento. Os ganhos do controlador são descritos como função de  $\varepsilon$  e  $t_s$  que, por sua vez, são parâmetros desejados e, portanto, dados de entrada no projeto.

No projeto do p-pll é necessário apenas o projeto do bloco LPF, já no LPN-pll faz-se necessário a realização do projeto do filtro NOTCH, um filtro rejeita-faixas de segunda ordem, projetado para atenuar ou rejeitar a componente do dobro da frequência fundamental da rede. A adição do filtro NOTCH no processo permite que os ganhos do controlador PI sejam menores, já que, agora, o processo de filtragem é atendido pelo NOTCH e o controlador cuida da regulação de frequência e fase do oscilador controlado por tensão. A função transferência do filtro NOTCH é apresentada em [3].

$$H_{Nf} = \frac{s^2 + 2\varepsilon_2 s + \omega_n^2}{s^2 + 2\varepsilon_1 s + \omega_n^2} [3]$$

Para que o filtro se comporte como um rejeita-faixas, o coeficiente de amortecimento  $\varepsilon_2$  tem de ser menor que o coeficiente de amortecimento  $\varepsilon_1$ . A frequência de ressonância ou de rejeição  $\omega_n$  deve ser alocada na segunda harmônica do sinal da rede.

Na tabela 1 são apresentados os dados de projeto, bem como os valores dos ganhos dos controladores PI. Na tabela 2 tem-se os parâmetros de projeto para o filtro NOTCH.

Tabela 1: Dados de Projeto

| Coeficientes  | p-pll    | LPN-pll  |

|---------------|----------|----------|

| $t_s$         | 0.1667ms | 0.0667ms |

| $\varepsilon$ | 0.7      | 0.7      |

| $K_i$         | 48       | 119.94   |

| $K_p$         | 1175.12  | 7339.35  |

Tabela 2: Dados de Projeto

|                 |          |

|-----------------|----------|

| $\omega_n$      | 753.9822 |

| $\varepsilon_1$ | 0.1      |

| $\varepsilon_2$ | 0.00001  |

## RESULTADOS E DISCUSSÃO

Após o projeto dos plls, a análise foi realizada tanto em testes de simulações como também no microcontrolador, para a validação dos dados.

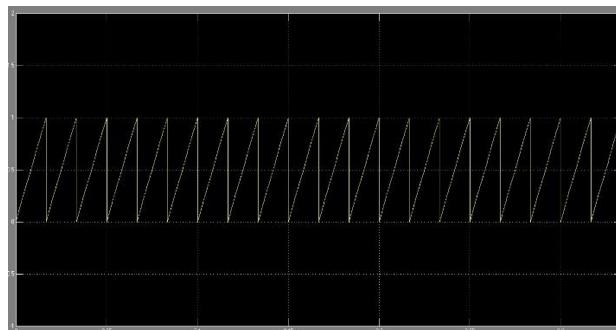

FIGURA2: p-pll simulado

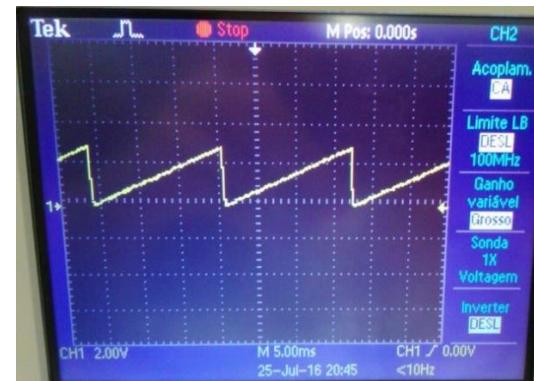

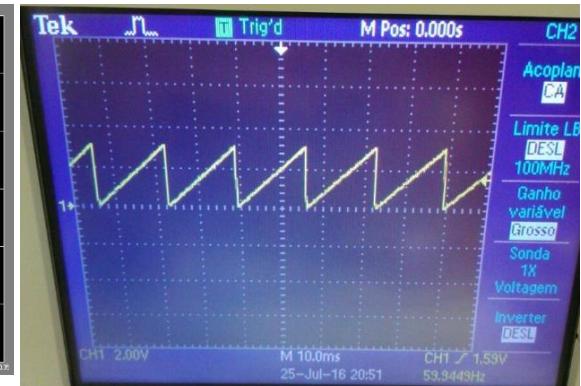

FIGURA3: p-pll prático

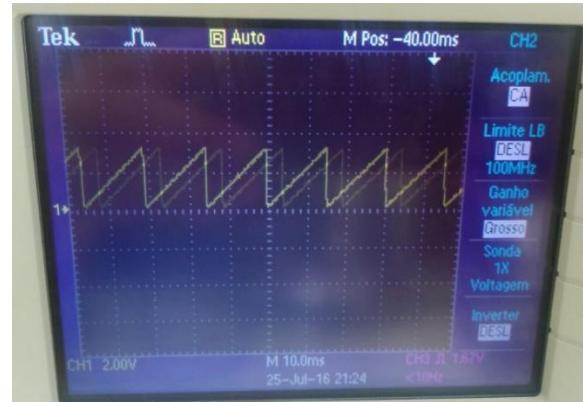

As figuras 2 e 3 mostram os resultados da rampa de sincronismo do p-pll, obtidos em simulação e experimentalmente. Os resultados práticos não foram conforme o esperado em simulação, da mesma forma podemos notar que no LPN-pll também obteve o mesmo funcionamento nas mesmas condições, ou seja em condições nominais da rede 60 Hz, mostrado nas figuras 4 e 5, os dois algoritmos em resultados práticos não foram satisfatórios.

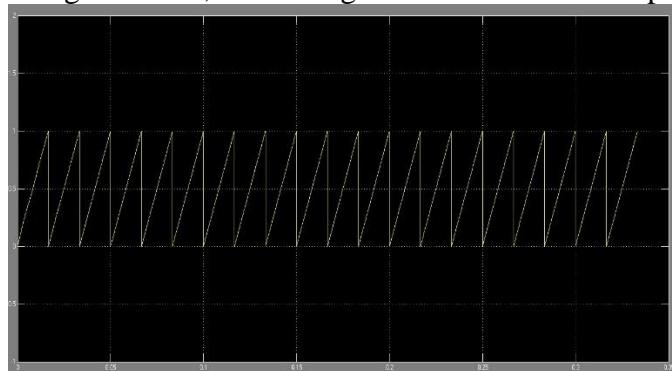

FIGURA4: LPN-pll simulado

FIGURA5: LPN-pll prático

Os plls foram submetidos a 3 testes de distúrbios comuns aos sistemas eletricos, são eles: afundamento de tensão, jumper de 65Hz na frequência e distorção harmonica. O tempo de estabelecimento de cada teste é mostrado na tabela 3 a seguir.

| Tabela 3: Teste de Distúrbios nos plls |          |         |          |          |

|----------------------------------------|----------|---------|----------|----------|

| Distúrbio                              | p-pll    |         | LPN-pll  |          |

|                                        | Simulado | Prático | Simulado | Prático  |

| Afundamento de 80%                     | 0ms      | 33.33ms | 50ms     | 200.00ms |

| Jumper de Frequência para 65Hz         | 35ms     | 210ms   | 20ms     | 110ms    |

O LPN-pll, apresentou melhor desempenho, no jumper de frequência, mas seu tempo de estabelecimento foi maior no afundamento de tensão, visto que seus ganhos no controlador foram projetados para um tempo de resposta menor que do p-pll, entretanto o funcionamento dos mesmo não tiveram o desempenho desejado.

Os mesmos pll, foram submetidos a testes de harmônicos e mostrados na figuras 6 e 7, nota-se se que mesmo na presença de harmônicos no sistema, o pll consegue sintetizar e produzir um sinal de referência, sem a interferencia da distorção.

FIGURA6: p-pll Hamonicos

FIGURA7: LPN-pll harmonicos

## CONCLUSÃO

Com a análise dos dois PLLs estudados nesse artigo, que no mesmo foi feito o estudo tanto por simulação como também por prática, não foi possível mostrar a proximidade dos modelos simulados e modelos reais realizados em laboratórios, porém a validação matemática dos algoritmos foi mostrada em simulação obtendo um bom desempenho, mesmo deparado com distúrbios comuns na rede elétrica, sempre foi possível detectar a freqüência fundamental da rede, que é o objetivo dos algoritmos plls. Outro resultado importante mostrando com os teste e que com a adição de um filtro NOTCH, pode se obter resultados mais eficazes quando comparado ao p-pll.

## REFERÊNCIAS BIBLIOGRAFICAS

GOMES, Pedro Henrique de castro. **Analise e Síntese de um Algoritmo “Phase-Locked-Loop” Robusto para Estimação de Amplitude, Ease e Erequência de Einais Elétricos**, 2007. Dissertação (mestrado em Engenharia Elétrica) Universidade Federal de Juiz de fora, Juiz de fora 2007.

MESQUISTA, Leon Marciel Oliveira de. **ESTUDO COMPARATIVO DE ALGORITMOS DE SINCRONIZAÇÃO COM APLICAÇÕES EM ELETRONICA DE POTÊNCIA**. Monografia (Grau de Engenheiro Eletricista) Universidade Federal do Rio de Janeiro, Rio de Janeiro, 2011.

SANTOS. L. A. GARCIA. V. B. SILVA. S. A. O. **Analise e Implementação de um Sistema PLL Utilizando DSP para Aplicações em Sistemas de Condicionamento de Energia**. UNOPAR Cient Exatas Tecnol. Londrina V.9 N. 1 p 5 – 12. Novembro de 2010.